# MIPS64<sup>TM</sup> 5K<sup>TM</sup> Processor Core Family Integrator's Guide

Document Number: MD00106 Revision 02.02 August 31, 2001

MIPS Technologies, Inc. 1225 Charleston Road Mountain View, CA 94043-1353

Copyright © 1999-2001 MIPS Technologies Inc. All right reserved.

Copyright © 1999-2001 MIPS Technologies, Inc. All rights reserved.

Unpublished rights reserved under the Copyright Laws of the United States of America.

This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying, reproducing, modifying, or use of this information (in whole or in part) which is not expressly permitted in writing by MIPS Technologies or a contractually-authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.

MIPS Technologies or any contractually-authorized third party reserves the right to change the information contained in this document to improve function, design or otherwise. MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error of omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability or fitness for a particular purpose, are excluded. Any license under patent rights or any other intellectual property rights owned by MIPS Technologies or third parties shall be conveyed by MIPS Technologies or any contractually-authorized third party in a separate license agreement between the parties.

The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto.

The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items. If the user of this information, or any related documentation of any kind, including related technical data or manuals, is an agency, department, or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation 12.212 for civilian agencies and Defense Federal Acquisition Regulation Supplement 227.7202 for military agencies. The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or any contractually-authorized third party.

MIPS<sup>®</sup>, R3000<sup>®</sup>, R4000<sup>®</sup>, R5000<sup>®</sup> and R10000<sup>®</sup> are among the registered trademarks of MIPS Technologies, Inc. in the United States and certain other countries, and MIPS16<sup>TM</sup>, MIPS16e<sup>TM</sup>, MIPS32<sup>TM</sup>, MIPS64<sup>TM</sup>, MIPS-3D<sup>TM</sup>, MIPS-based<sup>TM</sup>, MIPS II<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS III<sup>TM</sup>, MIPS IV<sup>TM</sup>, MIPS V<sup>TM</sup>, MDMX<sup>TM</sup>, SmartMIPS<sup>TM</sup>, 4Kr<sup>TM</sup>, 4Kc<sup>TM</sup>, 4Km<sup>TM</sup>, 4Ke<sup>TM</sup>, 4KEc<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KEp<sup>TM</sup>, 4KSr<sup>M</sup>, 4KSc<sup>TM</sup>, 5Kc<sup>TM</sup>, 5Kf<sup>TM</sup>, 20Kr<sup>M</sup>, 20Kc<sup>TM</sup>, R20K<sup>TM</sup>, R4300<sup>TM</sup>, ATLAS<sup>TM</sup>, CoreLV<sup>TM</sup>, JALGO<sup>TM</sup>, MALTA<sup>TM</sup>, MGB<sup>TM</sup>, SEAD<sup>TM</sup>, SEAD-2<sup>TM</sup>, SOC-it<sup>TM</sup> and YAMON<sup>TM</sup> are among the trademarks of MIPS Technologies, Inc.

All other trademarks referred to herein are the property of their respective owners.

# Table of Contents

| Chapter 1 Introduction                                 |    |

|--------------------------------------------------------|----|

| Chapter 2 EC Interface                                 |    |

| 2.1 Introduction                                       |    |

| 2.1.1 Features                                         |    |

| 2.1.2 Basic Operation                                  |    |

| 2.2 EC Interface Signal Descriptions                   | 5  |

| 2.3 Interface Transactions                             |    |

| 2.3.1 Single Read Transactions                         |    |

| 2.3.2 Single Write Transactions                        |    |

| 2.3.3 Back-to-back Read Transactions                   |    |

| 2.3.4 Back-to-back Write Transactions                  |    |

| 2.3.5 Read Transaction Followed by a Write Transaction | 14 |

| 2.3.6 Write Transaction Followed by a Read Transaction |    |

| 2.3.7 Burst Transactions                               |    |

| 2.4 External Write Buffers                             |    |

| 2.5 Endianess                                          |    |

| 2.6 Lower Address Bits                                 |    |

| Chapter 3 System Interface                             | 77 |

| 3.1 Introduction                                       |    |

| 3.2 System Interface Signal Descriptions               |    |

|                                                        |    |

| Chapter 4 Coprocessor Interface                        |    |

| 4.1 Introduction                                       |    |

| 4.2 Coprocessor Instructions                           |    |

| 4.3 Coprocessor Interface Signal Descriptions          |    |

| 4.4 Coprocessor Attachment to the 5K Family            |    |

| 4.4.1 5Kc Coprocessor Attachment                       |    |

| 4.4.2 5Kf Coprocessor Attachment                       |    |

| 4.4.3 COP2 Data Transfer Width                         |    |

| 4.4.4 Out-of-Order Data Transfers                      |    |

| 4.4.5 Limited Dual Issue                               |    |

| 4.5 Interface Protocols                                |    |

| 4.5.1 Instruction Dispatch                             |    |

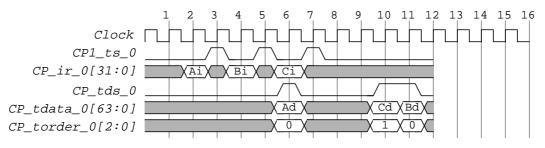

| 4.5.2 To Coprocessor Data Transfer                     |    |

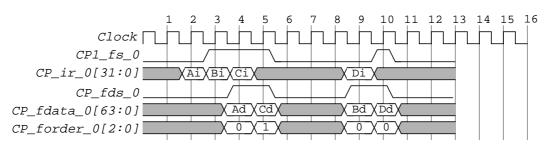

| 4.5.3 From Coprocessor Data Transfer                   |    |

| 4.5.4 Condition Code Checking                          |    |

| 4.5.5 GPR Data                                         |    |

| 4.5.6 Coprocessor Exceptions                           |    |

| 4.5.7 Instruction Nullification                        |    |

| 4.5.8 Instruction Killing                              |    |

| 4.5.9 Hardware Present Signaling                       |    |

| 4.5.10 Coprocessor Idle                                |    |

| 4.5.11 Reset                                           |    |

| Chapter 5 EJTAG Interface                              |    |

| 5.1 Introduction                                       |    |

| 5.2 EJTAG Interface Signal Descriptions                |    |

| 5.3 Test Access Port Interface Descriptions            |    |

| 5.3.1 TAP Reset                                        |    |

| 5.3.2 TAP Controller                                   |    |

|                                                        |    |

| 5.3.3 TAP Operation Example                         |     |

|-----------------------------------------------------|-----|

| 5.4 Reset from Probe                                |     |

| Charles C Deal address That I do for a              | (2) |

| Chapter 6 Production Test Interface                 |     |

| 6.2 Production Test Interface Signal Descriptions   |     |

| 6.3 Internal Scan Interface                         |     |

| 6.4 User-Implemented RAM BIST Interface             |     |

| 6.5 Integrated Memory BIST for Cache RAMs Interface |     |

| 0.5 Integrated Memory DIST for Cache RAWS Interface |     |

| Chapter 7 Clocking, Reset, and Power                |     |

| 7.1 Introduction                                    |     |

| 7.2 Clocking                                        |     |

| 7.2.1 SI_ClkIn Clock                                |     |

| 7.2.2 EJ_TCK Clock                                  |     |

| 7.2.3 Handling Clock Insertion Delay                |     |

| 7.3 Core Reset and NMI                              |     |

| 7.3.1 SI_ColdReset                                  |     |

| 7.3.2 SI_Reset                                      |     |

| 7.3.3 SI_NMI                                        |     |

| 7.4 Power Management                                |     |

| 7.4.1 Reducing SI_ClkIn Frequency                   |     |

| 7.4.2 Software-Induced Sleep Mode                   |     |

| Chapter 8 Simulation Models                         | 71  |

| 8.1 Installing the VMC Model                        |     |

| 8.2 Verifying the VMC Installation                  |     |

| 8.3 SWIFT Template Generation                       |     |

| 8.4 The MLOG test bench                             |     |

| 8.5 Back-annotating with SDF Timing                 |     |

| 8.6 Register Windows                                |     |

| 8.7 VMC Simulation Configuration                    |     |

| 8.8 Multiple VMC Instances                          |     |

| 8.9 Assertion Checks                                |     |

|                                                     |     |

| Appendix A Revision History                         |     |

# List of Figures

| Figure 2-1: Fastest Single Read Transaction Timing                                                    | 9  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2-2: Single Read Transaction Timing (3 Data Wait States)                                       | 10 |

| Figure 2-3: Fastest Single Write Transaction Timing                                                   | 11 |

| Figure 2-4: Single Write Transaction Timing (1 Address Wait State and 4 Data Wait States)             | 12 |

| Figure 2-5: Back-to-back Read Transaction Timing                                                      | 13 |

| Figure 2-6: Back-to-back Write Transaction Timing                                                     | 14 |

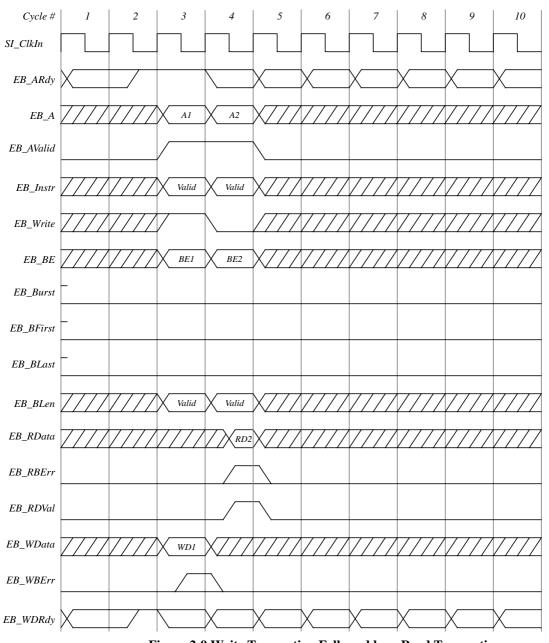

| Figure 2-7: Read Transaction Followed by a Write Transaction                                          |    |

| Figure 2-8: Read Transaction Followed by a Write Transaction with Reordering                          | 16 |

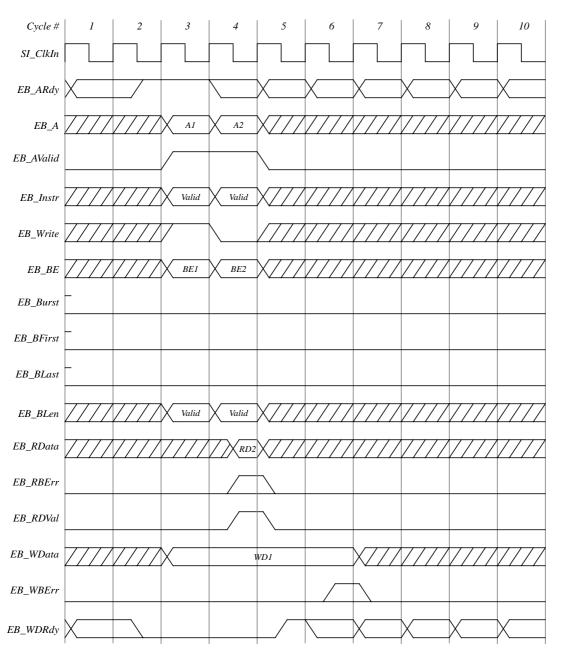

| Figure 2-9: Write Transaction Followed by a Read Transaction                                          | 17 |

| Figure 2-10: Write Transaction Followed by a Read Transaction with Reordering                         | 18 |

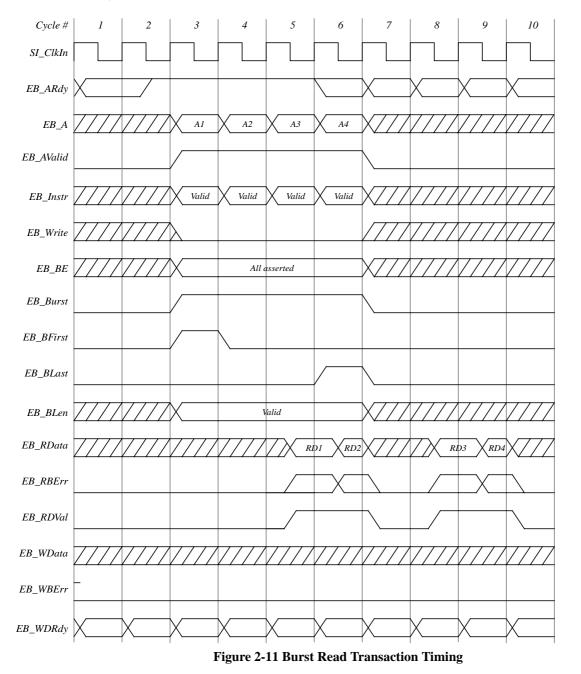

| Figure 2-11: Burst Read Transaction Timing                                                            | 19 |

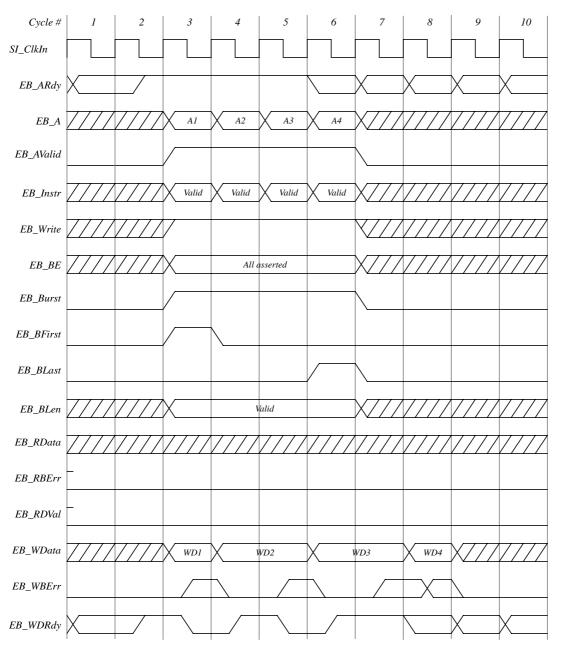

| Figure 2-12: Burst Write Transaction Timing                                                           |    |

| Figure 2-13: Example of EB_EWBE signalling when no wait states on address/data                        | 23 |

| Figure 2-14: Example of EB_EWBE signalling when no wait states on address and two wait states on data |    |

| Figure 2-15: Example of Generating Low Address Bits                                                   | 25 |

| Figure 4-1: Block Diagram of Coprocessor Interface                                                    | 41 |

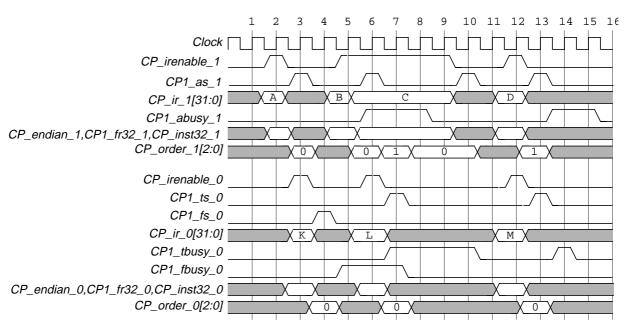

| Figure 4-2: General Transfer Example                                                                  |    |

| Figure 4-3: Arithmetic Coprocessor Dispatch Waveform                                                  |    |

| Figure 4-4: To Coprocessor Data Transfer Waveform                                                     |    |

| Figure 4-5: From Coprocessor Data Transfer Waveform                                                   | 50 |

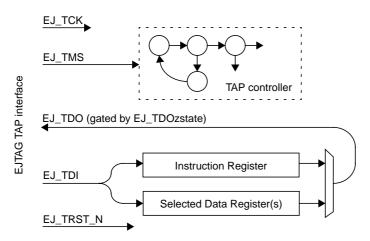

| Figure 5-1: Test Access Port (TAP) Overview                                                           | 58 |

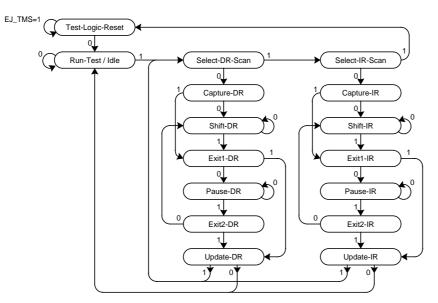

| Figure 5-2: TAP Controller State Diagram                                                              | 59 |

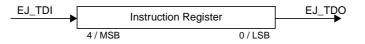

| Figure 5-3: EJ_TDI to EJ_TDO Path when in Shift-IR State                                              |    |

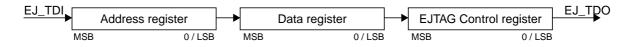

| Figure 5-4: EJ_TDI to EJ_TDO Path for Selected Data Register(s) when in Shift-DR State                |    |

| Figure 5-5: EJ_TDI to EJ_TDO Path when in Shift-DR State and ALL Instruction is Selected              | 61 |

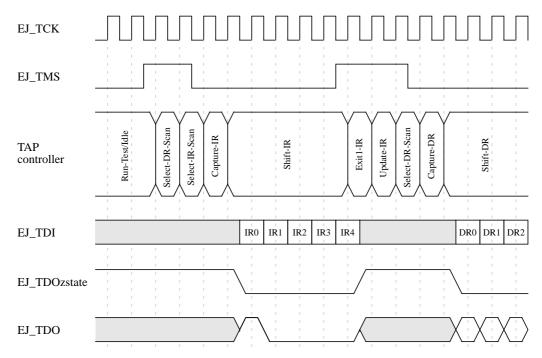

| Figure 5-6: TAP Operation Example                                                                     |    |

| Figure 6-1: Protocol for Use of Integrated Memory BIST for Cache RAMs                                 | 65 |

# List of Tables

| Table 2-1: Signal Direction Key                                             | 5  |

|-----------------------------------------------------------------------------|----|

| Table 2-1: Signal Direction Key         Table 2-2: EC Interface Signals     | 5  |

| Table 2-3: Burst Order for Sequential Ordering (4 Beat Bursts)              | 20 |

| Table 2-4: Burst Order for Sub-block Ordering (4 Beat Bursts)               |    |

| Table 2-5: Endian Examples                                                  | 24 |

| Table 3-1: Signal Direction Key                                             |    |

| Table 3-2: System Interface Signal Descriptions                             |    |

| Table 4-1: Signal Direction Key                                             |    |

| Table 4-2: Signal Coprocessor Category                                      |    |

| Table 4-3: Combined Issue Group 0 Signals - Used for both COP1 and COP2     |    |

| Table 4-4: Combined Issue Group 0 Signals - Used only for COP1              |    |

| Table 4-5: Combined Issue Group 0 Signals - Used only for COP2              |    |

| Table 4-6: Arithmetic Issue Group 1 Signals - Used for both COP1 and COP2   |    |

| Table 4-7: Arithmetic Issue Group 1 Signals - Used only for COP1            | 40 |

| Table 4-8: Arithmetic Issue Group 1 Signals - Used only for COP2            | 41 |

| Table 4-9: Transfers Required for Each Dispatch                             | 44 |

| Table 4-10: Allowable Interface Latencies from a Coprocessor to the 5K Core |    |

| Table 4-11: Interface Latencies From the 5K Core to a Coprocessor           | 46 |

| Table 5-1: Signal Direction Key                                             | 56 |

| Table 5-2: System Interface Signal Descriptions                             | 56 |

| Table 6-1: Signal Direction Key                                             | 63 |

| Table 6-2: Production Test Interface Signal Descriptions                    |    |

| Table 8-1: VMC Configuration Options                                        | 74 |

#### Chapter 1

# Introduction

The *MIPS64*  $5K^{TM}$  *Processor Core Family Integrator's Guide* is targeted for the ASIC designer who is integrating a version of the MIPS64 5K processor core into his/her system ASIC. This document is applicable to both those integrators who are using a hard core and those who are integrating a soft core.

The following chapters describe the interface to the 5K core, including descriptions of the pins of the core as well as a description of the protocols used:

- Chapter 2 describes the external system bus, EC<sup>TM</sup> interface, of the core.

- Chapter 3 describes the general system control signals used by the core.

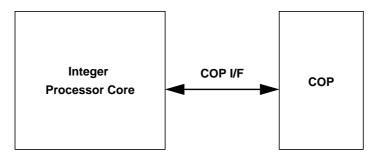

- Chapter 4 describes the COP interface used by the core for attaching tightly coupled coprocessor units.

- Chapter 5 describes the EJTAG interface used by the core, including the EJTAG TAP interface and controller.

- Chapter 6 describes the internal scan and memory test interface used by the core for production test.

- Chapter 7 describes how to properly clock and reset the core. Reset and power management is also covered in this chapter.

# EC Interface

This chapter describes the 5K EC interface, which allows the 5K core access to instruction and data memory as well as I/O devices. It contains the following sections:

- Section 2.1, "Introduction"

- Section 2.2, "EC Interface Signal Descriptions"

- Section 2.3, "Interface Transactions"

- Section 2.4, "External Write Buffers"

- Section 2.5, "Endianess"

- Section 2.6, "Lower Address Bits"

# 2.1 Introduction

The EC interface is implemented in the 5K core as follows:

- Data buses are 64 bits wide

- Address lines EB\_A[35:3] are used

- The maximum number of outstanding transactions is 17 (8 reads and 9 writes) when operating in default mode. In SimpleBE mode the maximum number of outstanding transactions is 25 (8 reads and 17 writes). SimpleBE mode is described in Section 2.4, "External Write Buffers" on page 21.

Also note the following 5K-specific feature: on a WAIT instruction, the 5K core waits until the internal write buffer is empty before entering low-power mode.

#### 2.1.1 Features

The 64-bit implementation of the EC interface has the following features:

- 64-bit data buses

- 36-bit addressing

- Separate read and write data buses

- All signals are unidirectional—no bidirectional or 3-state buses

- Fully registered, synchronous interface to the 5K core

- · Separate read and write bus error indications

- Separate address and data phases allow pipelining on the interface

- Number of outstanding transactions can be limited by the external logic

- · Sequential or sub-block ordering burst address sequences

- Indication of first and last address phase of a burst

- Request for emptying external write buffers and indication of external write buffers being empty

#### MIPS64™ 5K™ Processor Core Family Integrator's Guide, Revision 02.02

#### Copyright © 1999-2001 MIPS Technologies Inc. All right reserved.

- Byte enable indication

- Indication of instruction read (fetch)

- Address and data phases can complete the same cycle they are initiated (zero wait states)

- No limit on the number of wait states in address and data phases

- Independent read and write data phases. A read transaction can overtake a write transaction and vice versa.

- Only one 5K core and one external logic

#### 2.1.2 Basic Operation

All inputs to the 5K core are sampled at the rising edge of the SI\_ClkIn signal. Further the outputs from the 5K core change with respect to a rising edge of the SI\_ClkIn signal.

The EC interface does not include a signal to indicate reset. Therefore to reset the EC interface, reset the 5K core and the external logic simultaneously. Whenever the EC interface is reset, all transactions are aborted and the bus returns to the idle state. EB\_ARdy, EB\_AValid, EB\_WDRdy, EB\_RdVal, EB\_Burst, EB\_BFirst, EB\_BLast, EB\_RBErr, and EB\_WBErr must be driven inactive during reset.

Each transaction on the EC interface has an address phase and a data phase, which can have a number of wait states.

A wait state in the address phase is named an *address wait state* and is defined as a clock cycle where EB\_AValid is asserted and EB\_ARdy was sampled deasserted in the beginning of the cycle.

An address phase begins in the clock cycle where the 5K core asserts EB\_AValid. An address phase ends on the positive clock edge following an asserted sample of EB\_ARdy. For maximum speed (no address wait states), EB\_ARdy has to be sampled asserted on the positive clock edge preceding the beginning of the address phase. During an address phase, all signals driven by the 5K core are unchanged and stable (except from the write data bus, EB\_WData).

Due to the separate read and write data buses, two types of data phases exist: the read data phase and the write data phase.

A wait state in a data phase is named a *data wait state*. It is defined as a clock cycle where the corresponding address phase has been started (and possibly ended) and:

- For a write data phase, EB\_WDRdy is sampled deasserted at the beginning of the cycle

- For a read data phase, EB\_RdVal is sampled deasserted at the end of the cycle

A read data phase begins in the clock cycle where the 5K core starts the corresponding read address phase. However, if there are outstanding read data phases when the read address phase begins, the corresponding read data phase does not start until all of the preceding read data phases have ended. The read data phase ends at the positive clock edge where EB\_RdVal is sampled asserted. It can not end earlier than when the corresponding address phase ends.

A write data phase begins in the clock cycle where the 5K core starts the corresponding write address phase. However, if there are outstanding write data phases when the write address phase begins, the corresponding write data phase does not start until all of the preceding write data phases have ended. The write data phase ends at the positive clock edge following the positive clock edge where EB\_WDRdy is sampled asserted. For maximum speed (no data wait states), EB\_WDRdy must be asserted on the positive clock edge preceding the beginning of the corresponding address phase. It cannot end earlier than the corresponding address phase ends.

From these definitions, for a given transaction the number of data wait states must be greater than or equal to the number of address wait states.

# **2.2 EC Interface Signal Descriptions**

This section describes the signals of the 5K processor core's EC Interface. Table 2-1 provides the pin direction key for the signal descriptions. Note that all outputs are driven directly from flops and all inputs are input directly to flops. A clock cycle begins on a rising edge and ends just before the next rising edge.

| Table 2-1 | Signal | Direction | Key |

|-----------|--------|-----------|-----|

|-----------|--------|-----------|-----|

| Dir | Description                                                                                                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Ι   | Input to the 5K core. Unless otherwise noted, input signals are sampled on the rising edge of the appropriate CLK signal.                        |

| 0   | Output from the 5K core. Unless otherwise noted, output signals are driven on the rising edge of the appropriate CLK signal.                     |

| SI  | Static input to the 5K core. These signals are normally tied to either power or ground and should not change state while SI_Reset is deasserted. |

The signals are described in Table 2-2. Note that the signals are listed alphabetically.

| Signal Name | Dir | Description                                                                                                                                                                                                                               |

|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EB_A[35:3]  | 0   | Address bus. Only valid when EB_AValid is asserted.                                                                                                                                                                                       |

| EB_ARdy     | Ι   | Assertion of this signal indicates whether the external logic is ready for a new address. The 5K core does not complete the address phase until the clock cycle after EB_ARdy is sampled asserted.                                        |

| EB_AValid   | 0   | Assertion of this signal indicates that the values on the address bus and access type lines are valid (signifying an address phase is ongoing). EB_AValid is always valid and cannot be deasserted between address phases within a burst. |

#### **Table 2-2 EC Interface Signals**

| Signal Name           | Dir |                                                                                                                                                                                                                                                                          | Description                                                                                                                   |                                                                                                                                                                 |                                                                                                                       |                                                                                                                                    |                                                   |

|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

|                       |     | Indicates which bytes of the EB_RData or EB_WData buses are involved in the data phase corresponding to the current address phase. If an EB_BE signal is asserted, the associated byte is being read or written. EB_BE lines are only valid while EB_AValid is asserted. |                                                                                                                               |                                                                                                                                                                 |                                                                                                                       |                                                                                                                                    |                                                   |

|                       |     | During bursts a                                                                                                                                                                                                                                                          | ll lines mus                                                                                                                  | st be asserte                                                                                                                                                   | ed.                                                                                                                   |                                                                                                                                    |                                                   |

|                       |     | The table below SimpleBE mod                                                                                                                                                                                                                                             |                                                                                                                               | alues that E                                                                                                                                                    | B_BE ca                                                                                                               | n take in defa                                                                                                                     | ault mode and in                                  |

|                       |     |                                                                                                                                                                                                                                                                          | Byte enab                                                                                                                     | les supporte                                                                                                                                                    | d, SI_Sim                                                                                                             | pleBE[1:0]=0                                                                                                                       | )                                                 |

|                       |     | 00000001                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 0000010                                                                                                                                                         | 000                                                                                                                   | 00100                                                                                                                              | 00001000                                          |

|                       |     | 00010000                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 100000                                                                                                                                                          | 010                                                                                                                   | 00000                                                                                                                              | 10000000                                          |

|                       |     | 11000000                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 0110000                                                                                                                                                         | 000                                                                                                                   | 01100                                                                                                                              | 00000011                                          |

|                       |     | 11100000                                                                                                                                                                                                                                                                 | 01                                                                                                                            | 110000                                                                                                                                                          | 000                                                                                                                   | 01110                                                                                                                              | 00000111                                          |

|                       |     | 11110000                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 001111                                                                                                                                                          | 111                                                                                                                   | 11000                                                                                                                              | 00011111                                          |

|                       |     | 11111100                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 0111111                                                                                                                                                         | 111                                                                                                                   | 11110                                                                                                                              | 01111111                                          |

|                       |     | 11111111                                                                                                                                                                                                                                                                 |                                                                                                                               |                                                                                                                                                                 | 1                                                                                                                     |                                                                                                                                    |                                                   |

| EB_BE[7:0]            | 0   |                                                                                                                                                                                                                                                                          | Byte enab                                                                                                                     | les supporte                                                                                                                                                    | d, SI_Sim                                                                                                             | pleBE[1:0]=1                                                                                                                       |                                                   |

|                       |     | 00000001                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 0000010                                                                                                                                                         | 000                                                                                                                   | 00100                                                                                                                              | 00001000                                          |

|                       |     | 00010000                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 100000                                                                                                                                                          | 010                                                                                                                   | 00000                                                                                                                              | 10000000                                          |

|                       |     | 00000011                                                                                                                                                                                                                                                                 | 00                                                                                                                            | 001100                                                                                                                                                          | 001                                                                                                                   | 10000                                                                                                                              | 11000000                                          |

|                       |     | 00001111 11110000 11111111                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                                                                                                 |                                                                                                                       |                                                                                                                                    |                                                   |

|                       |     | EB_BE<br>Signal                                                                                                                                                                                                                                                          | Read D<br>Sam                                                                                                                 |                                                                                                                                                                 |                                                                                                                       | Data Bits<br>en Valid                                                                                                              | ]                                                 |

|                       |     | EB_BE[0]                                                                                                                                                                                                                                                                 | EB_RD                                                                                                                         | ata[7:0]                                                                                                                                                        | EB_W                                                                                                                  | /Data[7:0]                                                                                                                         |                                                   |

|                       |     | EB_BE[1]                                                                                                                                                                                                                                                                 | EB_RDa                                                                                                                        | ta[15:8]                                                                                                                                                        | EB_W                                                                                                                  | Data[15:8]                                                                                                                         |                                                   |

|                       |     | EB_BE[2]                                                                                                                                                                                                                                                                 | EB_RDa                                                                                                                        | ta[23:16]                                                                                                                                                       | EB_WI                                                                                                                 | Data[23:16]                                                                                                                        |                                                   |

|                       |     | EB_BE[3]                                                                                                                                                                                                                                                                 | EB_RDa                                                                                                                        | ta[31:24]                                                                                                                                                       | EB_WI                                                                                                                 | Data[31:24]                                                                                                                        |                                                   |

|                       |     | EB_BE[4]                                                                                                                                                                                                                                                                 | EB_RDa                                                                                                                        | ta[39:32]                                                                                                                                                       | EB WI                                                                                                                 | Data[39:32]                                                                                                                        |                                                   |

|                       |     |                                                                                                                                                                                                                                                                          |                                                                                                                               |                                                                                                                                                                 |                                                                                                                       | Jata[39.32]                                                                                                                        |                                                   |

|                       |     | EB_BE[5]                                                                                                                                                                                                                                                                 | EB_RDa                                                                                                                        | ta[47:40]                                                                                                                                                       |                                                                                                                       | Data[39:32]                                                                                                                        | _                                                 |

|                       |     | EB_BE[5]<br>EB_BE[6]                                                                                                                                                                                                                                                     | EB_RDa<br>EB_RDa                                                                                                              |                                                                                                                                                                 | EB_WI                                                                                                                 |                                                                                                                                    | -                                                 |

|                       |     |                                                                                                                                                                                                                                                                          |                                                                                                                               | ta[55:48]                                                                                                                                                       | EB_WI                                                                                                                 | Data[47:40]                                                                                                                        | -                                                 |

| EB_BFirst             | 0   | EB_BE[6]<br>EB_BE[7]                                                                                                                                                                                                                                                     | EB_RDa<br>EB_RDa<br>s signal inc                                                                                              | ta[55:48]<br>ta[63:56]<br>licates the a                                                                                                                         | EB_WI<br>EB_WI<br>EB_WI                                                                                               | Data[47:40]<br>Data[55:48]<br>Data[63:56]                                                                                          | st address phase of                               |

| EB_BFirst<br>EB_BLast | 0   | EB_BE[6]<br>EB_BE[7]<br>Assertion of thi<br>a burst. EB_BF<br>Assertion of thi                                                                                                                                                                                           | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>s signal inc<br>at the time                                               | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio                                                                           | EB_WI<br>EB_WI<br>eB_WI<br>ddress ph<br>uddress ph<br>n of EB_1                                                       | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>mase is the lass<br>BLast is dete                                 | st address phase of<br>rmined by use of           |

|                       |     | EB_BE[6]<br>EB_BE[7]<br>Assertion of thi<br>a burst. EB_BF<br>Assertion of thi<br>a burst. Note th<br>EB_Burst, EB_                                                                                                                                                      | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>is signal inc<br>at the time<br>BFirst, and<br>indicate the               | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio<br>EB_BLen.                                                               | EB_WI<br>EB_WI<br>EB_WI<br>ddress ph<br>ddress ph<br>n of EB_<br>EB_BLa<br>mber of ad                                 | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>ase is the last<br>BLast is dete<br>st is always<br>ddress/data p | st address phase of<br>rmined by use of           |

|                       |     | EB_BE[6]<br>EB_BE[7]<br>Assertion of thi<br>a burst. EB_BF<br>Assertion of thi<br>a burst. Note th<br>EB_Burst, EB_<br>EB_BLen[1:0]                                                                                                                                      | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>is signal inc<br>at the time<br>BFirst, and<br>indicate the<br>n implemer | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio<br>EB_BLen.                                                               | EB_WI<br>EB_WI<br>EB_WI<br>ddress ph<br>iddress ph<br>n of EB_<br>EB_BLa<br>mber of ad                                | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>ase is the last<br>BLast is dete<br>st is always<br>ddress/data p | st address phase of<br>rmined by use of<br>valid. |

|                       |     | EB_BE[6]<br>EB_BE[7]<br>Assertion of thi<br>a burst. EB_BF<br>Assertion of thi<br>a burst. Note th<br>EB_Burst, EB_<br>EB_BLen[1:0]<br>This signal is a                                                                                                                  | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>is signal inc<br>at the time<br>BFirst, and<br>indicate the<br>n implemer | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio<br>EB_BLen.<br>e length (nun<br>tation-spec                               | EB_WI<br>EB_WI<br>EB_WI<br>ddress ph<br>address ph<br>n of EB_J<br>EB_BLa<br>mber of ad<br>cific static<br>ength      | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>ase is the last<br>BLast is dete<br>st is always<br>ddress/data p | st address phase of<br>rmined by use of<br>valid. |

| EB_BLast              | 0   | EB_BE[6]<br>EB_BE[7]<br>Assertion of thi<br>a burst. EB_BF<br>Assertion of thi<br>a burst. Note th<br>EB_Burst, EB_<br>EB_BLen[1:0]<br>This signal is a<br>EB_BLeng                                                                                                      | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>is signal inc<br>at the time<br>BFirst, and<br>indicate the<br>n implemer | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio<br>EB_BLen.<br>e length (nun<br>tation-spec<br>Burst L                    | EB_WI<br>EB_WI<br>EB_WI<br>ddress ph<br>n of EB_:<br>EB_BLa<br>mber of a<br>ific static<br>ength<br>ved               | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>ase is the last<br>BLast is dete<br>st is always<br>ddress/data p | st address phase of<br>rmined by use of<br>valid. |

| EB_BLast              | 0   | EB_BE[6]         EB_BE[7]         Assertion of thi         a burst. EB_BF         Assertion of thi         a burst. Note th         EB_BLens         EB_BLens         EB_BLeng         0                                                                                 | EB_RDa<br>EB_RDa<br>s signal inc<br>irst is alwa<br>is signal inc<br>at the time<br>BFirst, and<br>indicate the<br>n implemer | ta[55:48]<br>ta[63:56]<br>licates the a<br>ys valid.<br>licates the a<br>for assertio<br>EB_BLen.<br>the length (num<br>tation-spector)<br>Burst L<br>resertion | EB_WI<br>EB_WI<br>EB_WI<br>ddress ph<br>uddress ph<br>n of EB_<br>EB_BLa<br>mber of ac<br>ific static<br>ength<br>ved | Data[47:40]<br>Data[55:48]<br>Data[63:56]<br>ase is the first<br>ase is the last<br>BLast is dete<br>st is always<br>ddress/data p | st address phase of<br>rmined by use of<br>valid. |

#### Table 2-2 EC Interface Signals (Continued)

| Signal Name     | Dir | Description                                                                                                                                                                                                                                                                                                                                              |  |  |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| EB_Burst        | 0   | Assertion of this signal indicates that the current address phase is for a cache fill or a write burst. EB_Burst is always valid.                                                                                                                                                                                                                        |  |  |

| EB_BusClkActive | Ι   | Must be driven HIGH                                                                                                                                                                                                                                                                                                                                      |  |  |

| EB_EWBE         | Ι   | Indicates that all external write buffers are empty. The external write buffers must deassert EB_EWBE in the cycle following the assertion of the corresponding EB_WDRdy and keep EB_EWBE deasserted until the external write buffers are empty. See Section 2.4, "External Write Buffers" on page 21 for more details.                                  |  |  |

| EB_Instr        | 0   | Assertion of this signal indicates that the address is for an instruction fetch as opposed to a data read. EB_Instr is only valid when EB_AValid is asserted.                                                                                                                                                                                            |  |  |

| EB_RBErr        | Ι   | Bus error indicator for read transactions. EB_RBErr is always valid. Only assert it in the same cycle that the corresponding EB_RdVal is asserted.                                                                                                                                                                                                       |  |  |

| EB_RData[63:0]  | Ι   | Read data bus. Valid at the end of a read data phase (on the rising clock edge where EB_RdVal is sampled asserted).                                                                                                                                                                                                                                      |  |  |

| EB_RdVal        | I   | Assertion of this signal indicates that the external logic is driving read data on EB_RData (it ends a read data phase). EB_RdVal must always be valid. EB_RdVal must never be asserted until after the corresponding EB_ARdy is sampled asserted.                                                                                                       |  |  |

| EB_SBlock       | SI  | When this signal is asserted, sub-block ordering is used for addressing bursts.<br>When this signal is deasserted, sequential addressing is used. See Section 2.3.7<br>"Burst Transactions" on page 18 for details.                                                                                                                                      |  |  |

| EB_WBErr        | I   | Bus error indicator for write transactions. EB_WBErr is always valid. Only assert it in the cycle following an asserted sample of the corresponding EB_WDRdy.                                                                                                                                                                                            |  |  |

| EB_WData[63:0]  | 0   | Write data bus. Kept unchanged and stable during a write data phase until the write data phase ends (the positive clock edge following an asserted sample of EB_WDRdy).                                                                                                                                                                                  |  |  |

| EB_WDRdy        | Ι   | Assertion of this signal indicates that the external logic is ready to process a write; it ends a write data phase and the EB_WData can change after the positive clock edge that follows the positive clock edge where EB_WDRdy is sampled asserted. EB_WDRdy is not sampled until the rising edge where the corresponding EB_ARdy is sampled asserted. |  |  |

| EB_Write        | 0   | Assertion of this signal indicates that the address phase is for a write.<br>Deassertion of this signal indicates that the address phase is for a read. This<br>signal is only valid when EB_AValid is asserted.                                                                                                                                         |  |  |

| EB_WWBE         | 0   | Assertion of this signal indicates that the 5K core is waiting for external write buffers to empty. EB_WWBE can be asserted when EB_EWBE is asserted, but if EB_EWBE is deasserted and EB_WWBE is asserted, EB_EWBE must be asserted eventually. See Section 2.4, "External Write Buffers" on page 21 for more details.                                  |  |  |

#### Table 2-2 EC Interface Signals (Continued)

# 2.3 Interface Transactions

The 5K core implements a unidirectional data-bus mode that uses separate busses for each direction. EB\_RData[63:0] is used for read operations, and EB\_WData[63:0] is used for write operations. The address phase of a bus transaction (all signals except the data transfer and bus error indication) is separated from the data phase (data transfer and bus error indication), that is, the address phase of a transaction can complete before the corresponding data phase begins.

The bus transactions listed below are described in the following subsections:

MIPS64™ 5K™ Processor Core Family Integrator's Guide, Revision 02.02

- Fastest read

- Single read with wait states

- · Fastest write

- Single write with wait states

- · Back-to-back read

- · Back-to-back write

- Read followed by write

- · Read followed by write with reordering

- Write followed by read

- · Write followed by read with reordering

- · Burst read

- Burst write

The 5K core supports the following outstanding bus transactions (adding up to a maximum of 17 outstanding transactions):

- 1 burst data read (4 reads) or a single data read

- 1 burst instruction read (4 reads) or a single instruction read

- 1 eviction of a dirty line (4 writes)

- 1 accelerated write burst (4 writes) or 5 single writes.

Note that the maximum number of outstanding single write transactions is 13 when operating in SimpleBE mode (adding up to a maximum of 25 outstanding transactions).

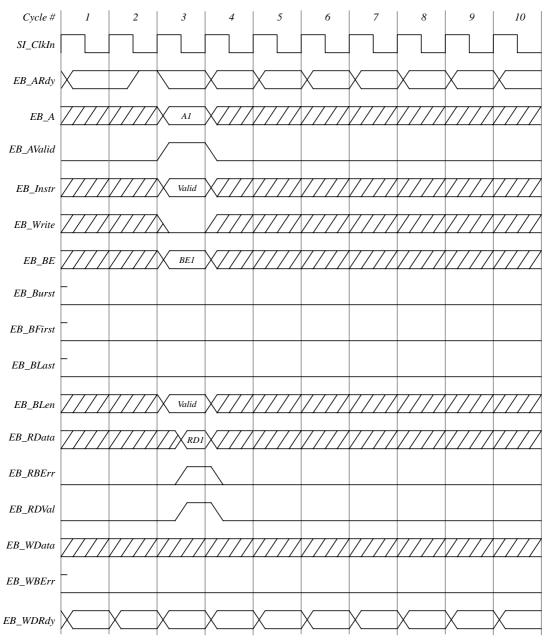

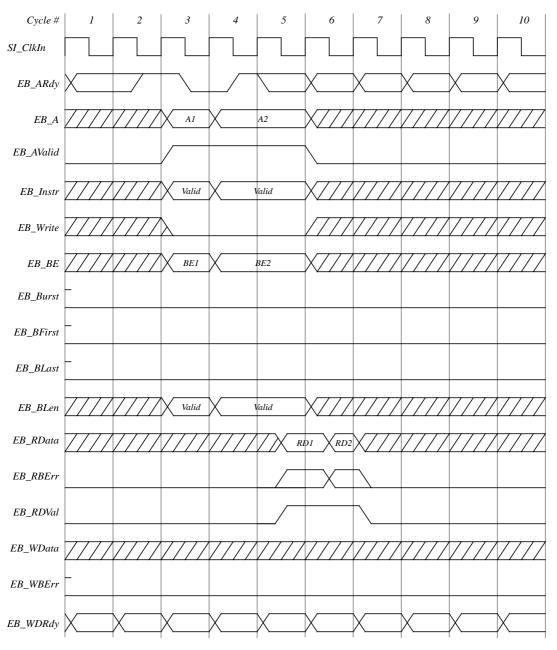

#### 2.3.1 Single Read Transactions

Figure 2-1 shows the basic timing relationships between signals during a simple (fastest) read transaction. When the 5K core is ready to begin a bus transaction (cycle 3), the address is driven on EB\_A, the associated control information is driven on EB\_Instr, EB\_Burst, EB\_BFirst, EB\_BLast, EB\_BLen, EB\_Write, and EB\_BE, and EB\_AValid is asserted. On the same rising clock edge that these signals are driven out (end of cycle 2), the EB\_ARdy signal state is sampled. If EB\_ARdy is sampled deasserted, the 5K core maintains the transaction values on the previously mentioned signals. The 5K core continues driving valid and stable values on these interface signals until the rising clock edge following the one that the EB\_ARdy signal is sampled asserted.

Starting in the same cycle as the read transaction is initiated, the 5K core samples EB\_RdVal, EB\_RData, and EB\_RBErr. These signals are sampled on each rising clock edge until the EB\_RdVal signal is sampled asserted. The data values sampled with this asserted EB\_RdVal are considered valid. However, if EB\_RBErr was sampled asserted in same cycle, the transaction is considered failed.

Note that the data phase cannot end earlier than the corresponding address phase. EB\_ARdy must be sampled asserted at least one clock cycle before the corresponding EB\_RdVal is sampled asserted.

Figure 2-1 Fastest Single Read Transaction Timing

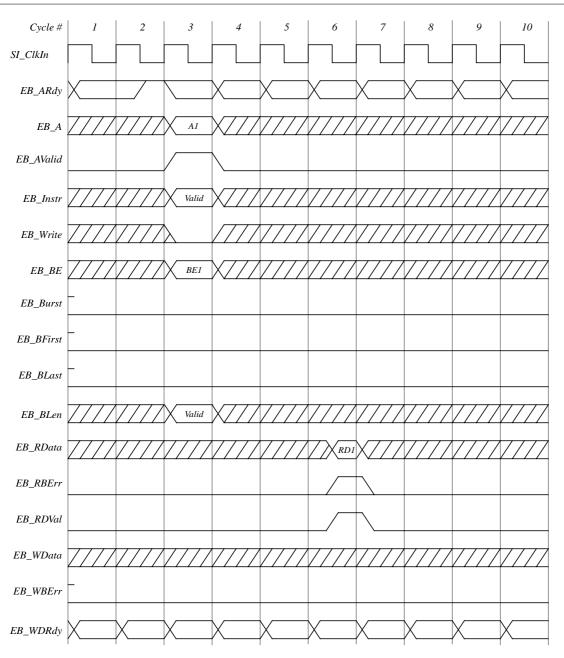

Figure 2-2 shows an example of a read transaction with three wait states in the data phase (indicated by the deassertion of EB\_RdVal for three clock cycles). EB\_RdVal is sampled deasserted on the rising edges at the beginning of cycles 4, 5, and 6 and then is asserted on cycle 7.

Figure 2-2 Single Read Transaction Timing (3 Data Wait States)

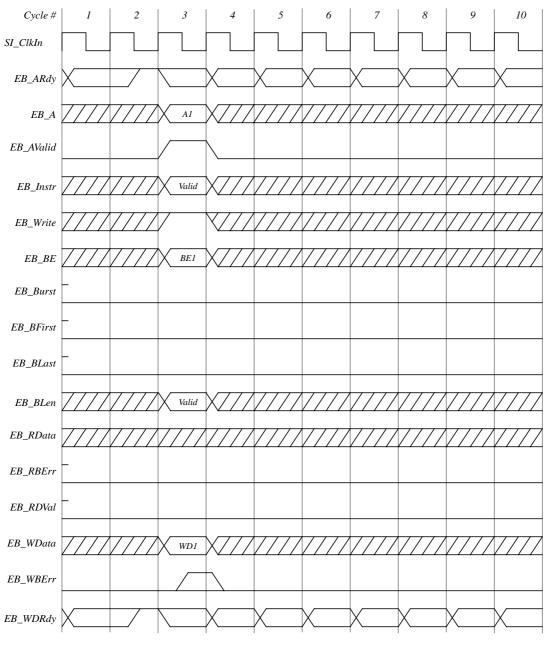

#### 2.3.2 Single Write Transactions

Figure 2-3 shows a zero wait state (fastest) write transaction. Like the read transaction when a write request is issued (cycle 3), the address and control information for the transaction are driven on EB\_A, EB\_Instr, EB\_Burst, EB\_BFirst, EB\_BLast, EB\_BLen, EB\_Write, and EB\_BE. These signals remain unchanged until the rising clock edge after the EB\_ARdy signal is sampled asserted.

The write data is driven on the write data bus, EB\_WData, in same cycle as the address is driven on EB\_A. The write data is held on the bus until the rising clock edge after EB\_WDRdy is sampled asserted.

EB\_WBErr is sampled on the first rising clock edge after the rising clock edge that EB\_WDRdy is sampled asserted. If EB\_WBErr is asserted at this time, the bus transaction is considered failed.

Note that the data phase cannot end earlier than the corresponding address phase. EB\_WDRdy must be sampled asserted on the same clock edge or later than the clock edge where the corresponding EB\_ARdy is sampled asserted.

Figure 2-3 Fastest Single Write Transaction Timing

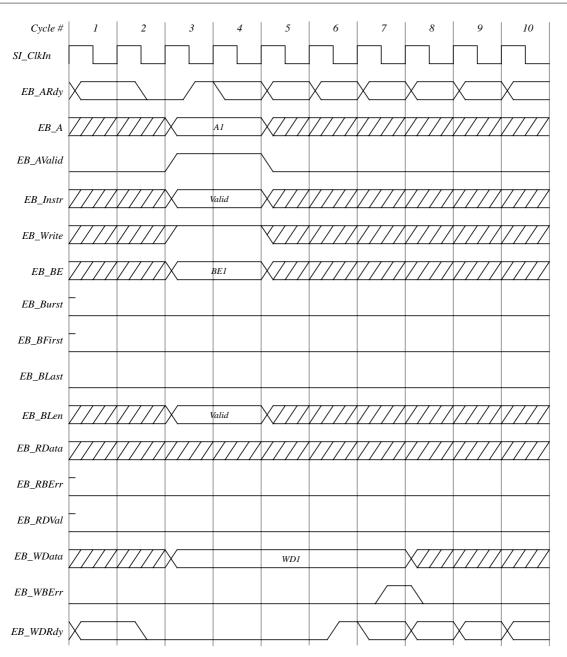

Figure 2-4 shows an example of a write transaction with four data wait states, indicated by the deassertion of the EB\_WDRdy signal. EB\_WDRdy is deasserted for four clock cycles, and then asserted. Note that the address phase is prolonged by one clock cycle because EB\_ARdy is deasserted for one clock cycle (sampled deasserted at the end of cycle 2).

Figure 2-4 Single Write Transaction Timing (1 Address Wait State and 4 Data Wait States)

#### 2.3.3 Back-to-back Read Transactions

Figure 2-5 shows an example of two consecutive read transactions, which shows the ability to pipeline read addresses independent of data wait states. Through manipulation of the EB\_ARdy signal, the external logic can limit the depth of the address pipelining.

Figure 2-5 Back-to-back Read Transaction Timing

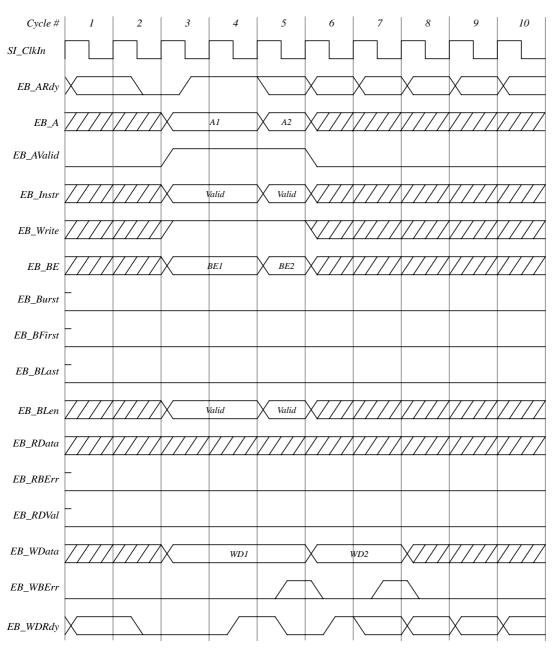

#### 2.3.4 Back-to-back Write Transactions

Figure 2-6 shows an example of two consecutive write transactions. Similar to the read transactions, pipelining of write addresses can occur regardless of data wait states.

Figure 2-6 Back-to-back Write Transaction Timing

#### 2.3.5 Read Transaction Followed by a Write Transaction

Figure 2-7 shows the relationship between a read transaction and a subsequent write transaction. A write transaction following a read transaction behaves as described for the single write transaction. Completion of these transactions out of order is allowed.

Figure 2-7 Read Transaction Followed by a Write Transaction

Figure 2-8 shows an example of a read transaction followed by a write transaction where the write transaction is completed prior to the read transaction (out of order).

Figure 2-8 Read Transaction Followed by a Write Transaction with Reordering

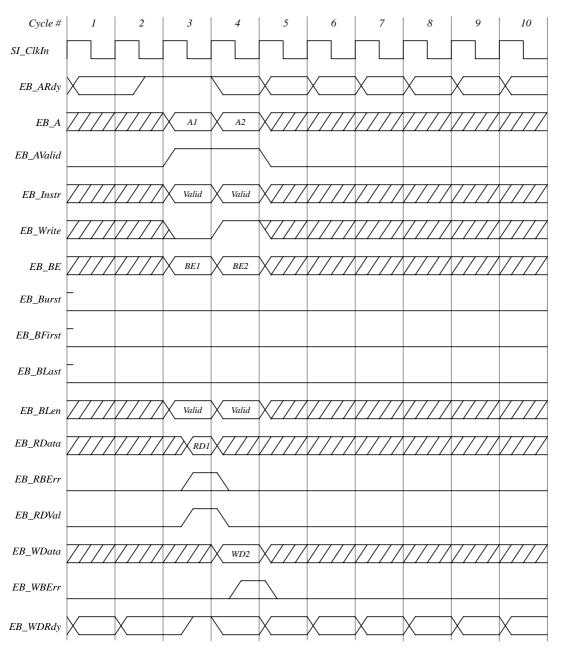

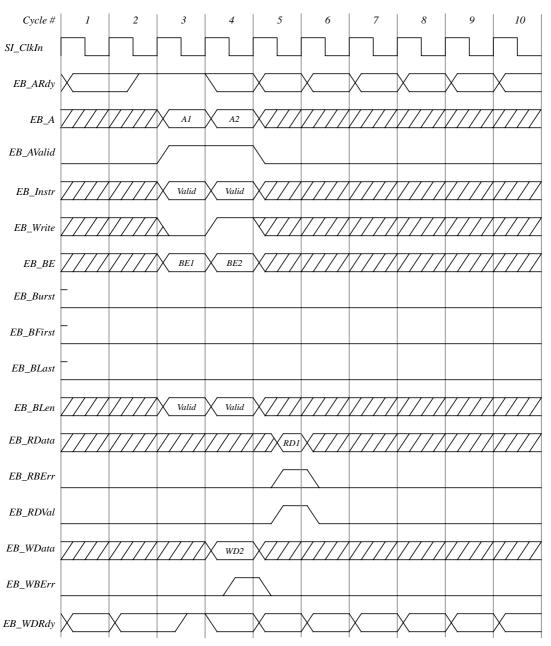

#### 2.3.6 Write Transaction Followed by a Read Transaction

Figure 2-9 shows an example of a write transaction followed by a read. As in the case of a write following a read, a read transaction following a write transaction is not affected by the behavior of the write transaction. Completion of these transactions out of order is allowed.

Figure 2-9 Write Transaction Followed by a Read Transaction

Figure 2-10 shows an example of a write transaction followed by a read transaction where the read transaction is completed prior to the write transaction (out of order).

Figure 2-10 Write Transaction Followed by a Read Transaction with Reordering

#### 2.3.7 Burst Transactions

A burst transaction initiates the transfer of multiple related transfers. Read bursts are used to read data to be placed in the instruction or data cache. Write bursts are used to empty the contents of the write buffers.

Note that initiated bursts are always completed. The burst transaction cannot be aborted before reaching the burst beat count (indicated by EB\_BLen) except in the case where the EC interface is reset.

EB\_Burst is asserted during the entire burst address sequence. EB\_BFirst is driven asserted during the first address phase of the burst and is deasserted with each of the remaining address phases. EB\_BLast is driven asserted during the last address phase and is deasserted with all prior address phases. Apart from EB\_Burst, EB\_BFirst and EB\_BLast behavior, and the deterministic address sequence, the multiple transfers of a burst transaction behave like that of back-to-back

18

single transactions, which simplifies interfacing to systems that do not support burst transactions. Note that it is possible in the presence of data wait states, for all of the burst address phases to complete before the first data phase of the burst (or even of a preceding transaction) has completed. If this behavior is undesirable, EB\_ARdy can be used to control the pace at which the addresses are transferred.

Note that EB\_AValid cannot be deasserted between address phases within a burst and that all bits in EB\_BE must be asserted in all address phases within a burst.

Figure 2-11 shows an example of a read burst transaction. EB\_BLen indicates the length of the burst (see Section 2.2, "EC Interface Signal Descriptions" on page 5 for further information on EB\_BLen). The data requested is always an aligned block according to the EB\_BLen signal. The order of the words within the block varies depending on which word in the block is being requested and the value of EB\_SBlock (see Table 2-3 and Table 2-4 for further information on the refill scheme).

MIPS64<sup>™</sup> 5K<sup>™</sup> Processor Core Family Integrator's Guide, Revision 02.02

Table 2-3 and Table 2-4 show the possible sequences for the least significant address bits during a burst. Note that addresses within a write burst will always be sequential and ascending matching the first rows in the following tables.

| Req DWord<br>Address | (EB_A[4:3]) Sequence |   |   |   |  |

|----------------------|----------------------|---|---|---|--|

| 0                    | 0                    | 1 | 2 | 3 |  |

| 1                    | 1                    | 2 | 3 | 0 |  |

| 2                    | 2                    | 3 | 0 | 1 |  |

| 3                    | 3                    | 0 | 1 | 2 |  |

Table 2-3 Burst Order for Sequential Ordering (4 Beat Bursts)

Table 2-4 Burst Order for Sub-block Ordering (4 Beat Bursts)

| Req DWord<br>Address | (EB_A[4:3]) Sequence |   |   |   |  |

|----------------------|----------------------|---|---|---|--|

| 0                    | 0                    | 1 | 2 | 3 |  |

| 1                    | 1                    | 0 | 3 | 2 |  |

| 2                    | 2                    | 3 | 0 | 1 |  |

| 3                    | 3                    | 2 | 1 | 0 |  |

Figure 2-12 shows a burst write. Burst write transactions are used to empty write buffers. Write burst addresses always start at the lowest address of an address block according to the EB\_BLen indication.

Note that like single transactions, burst read and write transactions can complete out of order. Burst reads can overtake burst writes and vice versa.

Figure 2-12 Burst Write Transaction Timing

### 2.4 External Write Buffers

Load and store instructions can generate bus transactions with byte enable patterns that are not directly supportable on other bus standards. To facilitate connection to these types of busses, the core has a mode where it will only generate bus transactions that are naturally aligned bytes, half-words, words, or dwords. This is referred to as SimpleBE mode, selected when SI\_SimpleBE[1:0] is set to 2b01. The default mode for the EC interface, in which the full range of byte enable combinations may occur, is selected when SI\_SimpleBE[1:0] is set to 2b00. Note that the SI\_SimpleBE bus is a static input which must be set to DC values at power-up of the core. The other two possible values of SI\_SimpleBE are currently reserved and should not be selected. The valid byte enable patterns in both SimpleBE mode and default mode are listed EB\_BE description in Table 2-2 on page 5.

The load instructions which attempts to generate a complex byte enable combination are uncached LWL, LWR, LDL, and LDR instructions. These instructions can generate 3, 5, 6, and 7 byte requests besides the naturally aligned bytes, half-words, words, or dwords. In SimpleBE mode, these transaction will be turned into a word or dword request on the interface. When the full word/dword is returned, the core will only use the appropriate bytes. In normal mode, load operations to uncached space are always for the exact bytes requested. In SimpleBE mode, however, uncached 3, 5, 6, and 7 byte loads are turned into a full word/dword request, so the memory system must be capable of tolerating an uncached request to the full word/dword even when the core will only use part of the word/dword.

SWL/SWR/SDL/SDR instructions can also attempt to generate complex byte enable combinations. When a write transaction with complex byte enables is detected internally, the core will split the write into two or three transactions on the bus, each of which meets one of the SimpleBE mode byte enable combinations shown in Table 2-2. A 7 byte write will be split into three transactions and 3, 5, and 6 byte writes will be split into two transactions before the writes are issued on the EC interface.

Some systems might have external write buffers to increase bus efficiency and system performance. The 5K core has a two-signal interface that allows software to have some control over the external write buffers. The SYNC instruction is intended to form a barrier between load/store instructions before and after it in the instruction stream. Upon execution of a SYNC instruction, the 5K core completes all pending read requests and flush the internal write buffer. The 5K core also asserts EB\_WWBE to signal to the system that it is Waiting for the Write Buffer Empty signal. The SYNC instruction does not complete until the EB\_EWBE input is asserted.

In most systems you can tie EB\_EWBE high. Just using EB\_WWBE does not ensure coherency. If a write is in the external write buffer, the core can generate a read request to the given address without asserting EB\_WWBE (because the core has no knowledge of the external write buffers). Therefore, any write buffers in the system must maintain coherency with reads.

The EB\_WWBE/EB\_EWBE interface can be used to make SYNCs "harder" by forcing the flush of the external write buffers in addition to flushing internal write buffers.

This method is a system/software design issue—you need to decide what if anything you want the system to do when a SYNC instruction is executed.

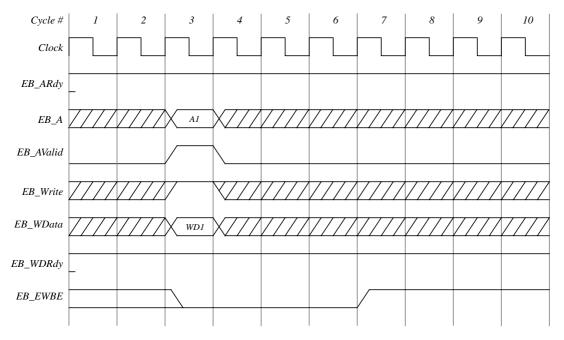

In Figure 2-13 and Figure 2-14 two examples of EB\_EWBE signalling are shown. When there are no wait states on the write transactions (Figure 2-13) EB\_EWBE must be deasserted when EB\_AValid and EB\_Write is asserted or if the external write buffer are non-empty due to previous write transactions. In Figure 2-13 EB\_EWBE is asserted in cycle 7 as no writes are received and the external write buffers are empty.

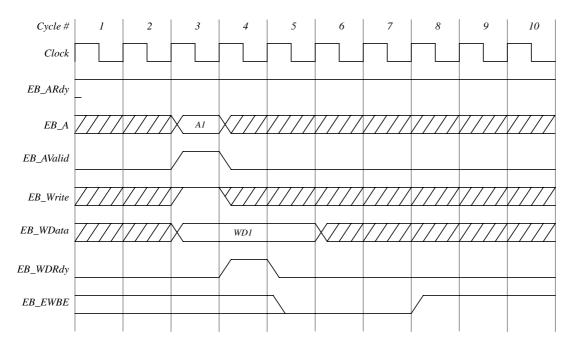

In Figure 2-14 two wait states are inserted in the data phase. EB\_EWBE is deasserted one cycle after assertion of EB\_WDRdy. In the example EB\_WDRdy is asserted due to acceptance of a new write transaction and EB\_EWBE is deasserted in cycle 5 as EB\_WDRdy was asserted in cycle 4. In Figure 2-14 EB\_EWBE is asserted in cycle 8 as no writes are received and the external write buffers are empty.

Note that the number of cycles where EB\_EWBE is deassserted will depend on the actual implementation of the external write buffers.

Figure 2-13 Example of EB\_EWBE signalling when no wait states on address/data.

Figure 2-14 Example of EB\_EWBE signalling when no wait states on address and two wait states on data.

# 2.5 Endianess

To help understand the use of endianess, Table 2-5 shows some cases of how stores appear on the EC interface in little-endian and big-endian mode.

|                                                                                                                        | Internal  | Big-endian            | Little-endian  |                                        |                |

|------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|----------------|----------------------------------------|----------------|

|                                                                                                                        | Addr[2:0] | EB_D[63:0]            | EB_BE<br>[7:0] | EB_D[63:0]                             | EB_BE<br>[7:0] |

| lui t0, 0x0123<br>ori t0, t0, 0x4567<br>dsll t0, t0, 16<br>ori t0, t0, 0x89ab<br>dsll t0, t0, 16<br>ori t0, t0, 0xcdef | )         |                       | <u>-</u>       |                                        |                |

| sb t0, 0x0(r0)                                                                                                         | 0         | 0xefXXXXXXXXXXXXXXXXX | 1000000        | 0xXXXXXXXXXXXXXXXX                     | 00000001       |

| sb t0, 0x1(r0)                                                                                                         | 1         | 0xXXefXXXXXXXXXXXXX   | 01000000       | 0xXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | 00000010       |

| sb t0, 0x2(r0)                                                                                                         | 2         | 0xXXXXefXXXXXXXXXX    | 00100000       | 0xXXXXXXXXXXXefXXXX                    | 00000100       |

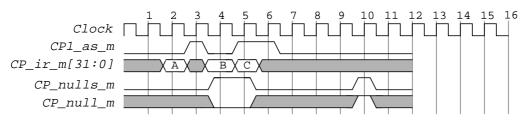

| sb t0, 0x3(r0)                                                                                                         | 3         | 0xXXXXXXXefXXXXXXXX   | 00010000       | 0xXXXXXXXXXefXXXXXX                    | 00001000       |